- 您现在的位置:买卖IC网 > Sheet目录2000 > IDT5V49EE902NLGI (IDT, Integrated Device Technology Inc)IC CLOCK GEN PLL 500MHZ 32VFQFPN

IDT5V49EE902

EEPROM PROGRAMMABLE CLOCK GENERATOR

CLOCK SYNTHESIZER

IDT EEPROM PROGRAMMABLE CLOCK GENERATOR

24

IDT5V49EE902

REV P 092412

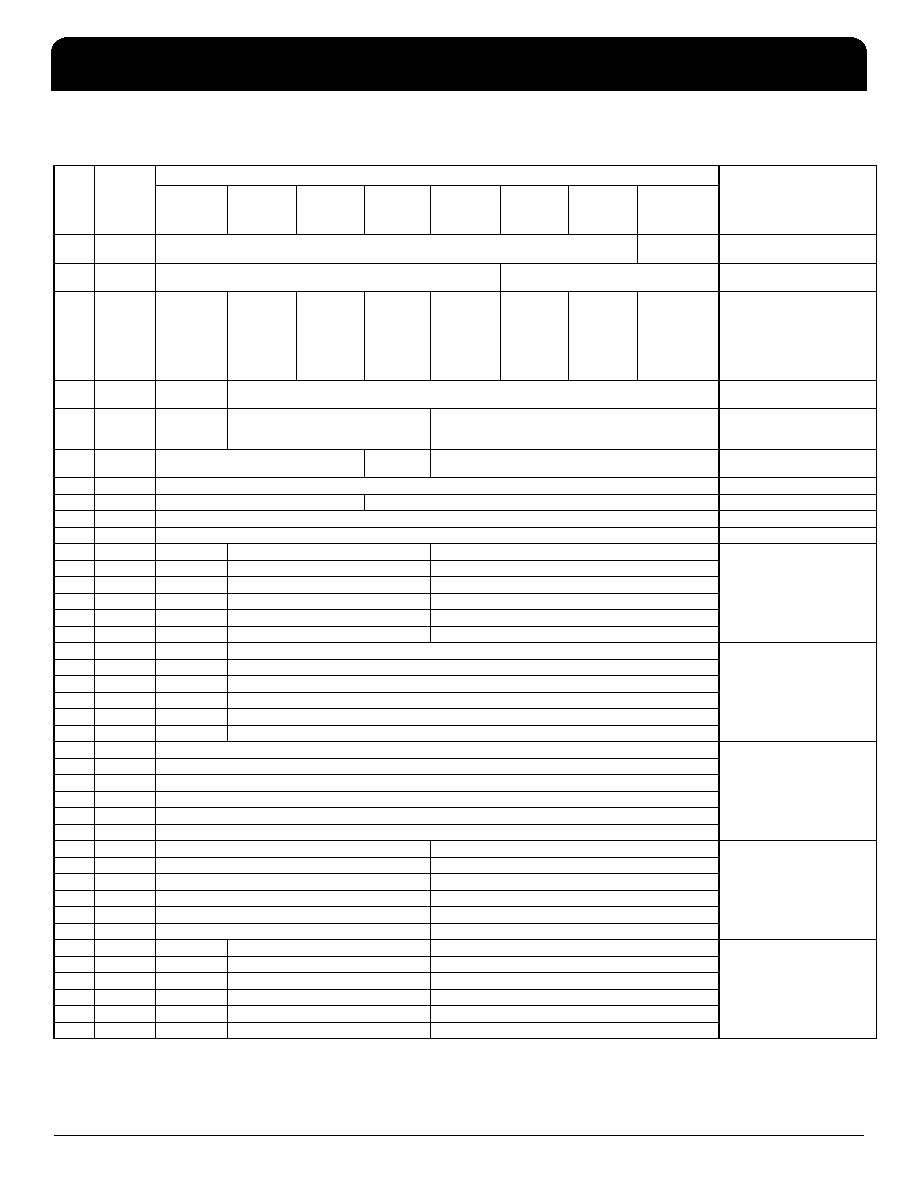

Programming Registers Table

Addr

Default

Register

Hex

Value

Bit #

Description

76

5

4

3

2

1

0

0x00

00

Reserved

HW/SW

Hardware/Software Mode control

HW/SW - 0=HW, 1=SW

0x01

00

Reserved

SEL[2:0]

SEL[2:0] - selects configuration in

SW mode

0x02

02

SP

OE6

OE5

OE4

OE3

OE2

OE1

OE0

OEx=Output Power Suspend

function for OUTx (‘1’=OUTx will

be suspended on SD/OE pin.

Disable mode is defined by

OEMx bits), ‘0’=outputs enabled

and no association with OE pin

(default).

0x03

02

Reserved

OS*[6:0]

OS*[6:0] - output suspend, active

low. Overwrites OE setting.

0x04

0F

SH

Reserved

PLLS*[3:0]

PLLS*[3:0] - PLL Suspend, active

low

SH - shutdown/OE configuration

0x05

04

Reserved

XTCLKSEL

Reserved

XTCLKSEL - crystal/clock select.

0=Crytal, 1=ICLK

0x06

00

Reserved

0x07

00

Reserved

XTAL[4:0]

XTAL[4:0] - crystal cap

0x08

00

Reserved

0x09

00

Reserved

0x0A

10

CZ0_CFG4

IP0[2:0]_CFG4

RZ0[3:0]_CFG4

PLL0 loop parameter

0x0B

10

CZ0_CFG5

IP0[2:0]_CFG5

RZ0[3:0]_CFG5

0x0C

10

CZ0_CFG0

IP0[2:0]_CFG0

RZ0[3:0]_CFG0

0x0D

10

CZ0_CFG1

IP0[2:0]_CFG1

RZ0[3:0]_CFG1

0x0E

10

CZ0_CFG2

IP0[2:0]_CFG2

RZ0[3:0]_CFG2

0x0F

10

CZ0_CFG3

IP0[2:0]_CFG3

RZ0[3:0]_CFG3

0x10

00

Reserved

D0[6:0]_CFG0

PLL0 input divider and input sel

D0[6:0] - 127 step Ref Div

D0 = 0 means power down.

0x11

00

Reserved

D0[6:0]_CFG1

0x12

00

Reserved

D0[6:0]_CFG2

0x13

00

Reserved

D0[6:0]_CFG3

0x14

00

Reserved

D0[6:0]_CFG4

0x15

00

Reserved

D0[6:0]_CFG5

0x16

01

N0[7:0]_CFG4

N - Feedback Divider

2 - 4095 (values of “0” and “1” are

not allowed) Total feedback with

A, using provided calculation

0x17

01

N0[7:0]_CFG5

0x18

01

N0[7:0]_CFG0

0x19

01

N0[7:0]_CFG1

0x1A

01

N0[7:0]_CFG2

0x1B

01

N0[7:0]_CFG3

0x1C

00

A0[3:0]_CFG0

N0[11:8]_CFG0

0x1D

00

A0[3:0]_CFG1

N0[11:8]_CFG1

0x1E

00

A0[3:0]_CFG2

N0[11:8]_CFG2

0x1F

00

A0[3:0]_CFG3

N0[11:8]_CFG3

0x20

00

A0[3:0]_CFG4

N0[11:8]_CFG4

0x21

00

A0[3:0]_CFG5

N0[11:8]_CFG5

0x22

10

CZ1_CFG4

IP1[2:0]_CFG4

RZ1[3:0]_CFG4

PLL1 Loop Parameter

0x23

10

CZ1_CFG5

IP1[2:0]_CFG5

RZ1[3:0]_CFG5

0x24

10

CZ1_CFG0

IP1[2:0]_CFG0

RZ1[3:0]_CFG0

0x25

10

CZ1_CFG1

IP1[2:0]_CFG1

RZ1[3:0]_CFG1

0x26

10

CZ1_CFG2

IP1[2:0]_CFG2

RZ1[3:0]_CFG2

0x27

10

CZ1_CFG3

IP1[2:0]_CFG3

RZ1[3:0]_CFG3

发布紧急采购,3分钟左右您将得到回复。

相关PDF资料

IDT5V49EE904NLGI8

IC PLL CLK GEN 200MHZ 32VFQFN

IDT821024PPG

IC PCM CODEC QUAD NONPROG 44TQFP

IDT821034DNG

IC PCM CODEC QUAD MPI 52-PQFP

IDT821054PQF

IC PCM CODEC QUAD MPI 64-PQFP

IDT82V3001APVG8

IC PLL WAN W/SGL REF INP 56-SSOP

IDT82V3010PVG

IC PLL WAN 51/E1/OC3 DUAL 56SSOP

IDT82V3011PVG

IC PLL WAN T1/E1/OC3 SGL 56-SSOP

IDT82V3012PVG8

IC PLL WAN T1/E1/OC3 DUAL 56SSOP

相关代理商/技术参数

IDT5V49EE902NLGI8

制造商:Integrated Device Technology Inc 功能描述:IC CLK GEN EEPROM PROGR 32QFN

IDT5V49EE903NLGI

制造商:Integrated Device Technology Inc 功能描述:IC CLOCK GENERATOR

IDT5V49EE903NLGI8

制造商:Integrated Device Technology Inc 功能描述:IC CLK GEN EEPROM PROGR 32QFN

IDT5V49EE903PGGI

制造商:Integrated Device Technology Inc 功能描述:IC CLOCK GENERATOR

IDT5V49EE903PGGI8

制造商:Integrated Device Technology Inc 功能描述:IC CLK GEN EEPROM PROGR 28TSSOP

IDT5V49EE904NLGI

功能描述:IC PLL CLK GEN 200MHZ 32VFQFN RoHS:是 类别:集成电路 (IC) >> 时钟/计时 - 时钟发生器,PLL,频率合成器 系列:VersaClock™ III 标准包装:2,000 系列:- 类型:PLL 频率合成器 PLL:是 输入:晶体 输出:时钟 电路数:1 比率 - 输入:输出:1:1 差分 - 输入:输出:无/无 频率 - 最大:1GHz 除法器/乘法器:是/无 电源电压:4.5 V ~ 5.5 V 工作温度:-20°C ~ 85°C 安装类型:表面贴装 封装/外壳:16-LSSOP(0.175",4.40mm 宽) 供应商设备封装:16-SSOP 包装:带卷 (TR) 其它名称:NJW1504V-TE1-NDNJW1504V-TE1TR

IDT5V49EE904NLGI8

功能描述:IC PLL CLK GEN 200MHZ 32VFQFN RoHS:是 类别:集成电路 (IC) >> 时钟/计时 - 时钟发生器,PLL,频率合成器 系列:VersaClock™ III 标准包装:1,000 系列:- 类型:时钟/频率合成器,扇出分配 PLL:- 输入:- 输出:- 电路数:- 比率 - 输入:输出:- 差分 - 输入:输出:- 频率 - 最大:- 除法器/乘法器:- 电源电压:- 工作温度:- 安装类型:表面贴装 封装/外壳:56-VFQFN 裸露焊盘 供应商设备封装:56-VFQFP-EP(8x8) 包装:带卷 (TR) 其它名称:844S012AKI-01LFT

IDT5V50009DCG

功能描述:IC PC CLOCK 8-SOIC RoHS:是 类别:集成电路 (IC) >> 时钟/计时 - 时钟发生器,PLL,频率合成器 系列:- 标准包装:39 系列:- 类型:* PLL:带旁路 输入:时钟 输出:时钟 电路数:1 比率 - 输入:输出:1:10 差分 - 输入:输出:是/是 频率 - 最大:170MHz 除法器/乘法器:无/无 电源电压:2.375 V ~ 3.465 V 工作温度:0°C ~ 70°C 安装类型:* 封装/外壳:* 供应商设备封装:* 包装:*